- 您现在的位置:买卖IC网 > Sheet目录3887 > PIC16F872T-E/SO (Microchip Technology)IC MCU CMOS 20MHZ 2K FLSH 28SOIC

130

8048C–AVR–02/12

ATtiny43U

When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a con-

version on a positive edge of the selected trigger signal. The trigger source is selected by setting

the ADC Trigger Select bits, ADTS in ADCSRB.

Bit 4 – ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the data registers are updated. The ADC

Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set. ADIF is

cleared by hardware when executing the corresponding interrupt handling vector. Alternatively,

ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify-Write on

ADCSRA, a pending interrupt can be disabled. This also applies if the SBI instruction is used.

Bit 3 – ADIE: ADC Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Inter-

rupt is activated.

Bits 2:0 – ADPS[2:0]: ADC Prescaler Select Bits

These bits determine the division factor between the system clock frequency and the input clock

to the ADC.

16.13.3

ADCL and ADCH – ADC Data Register

16.13.3.1

ADLAR = 0

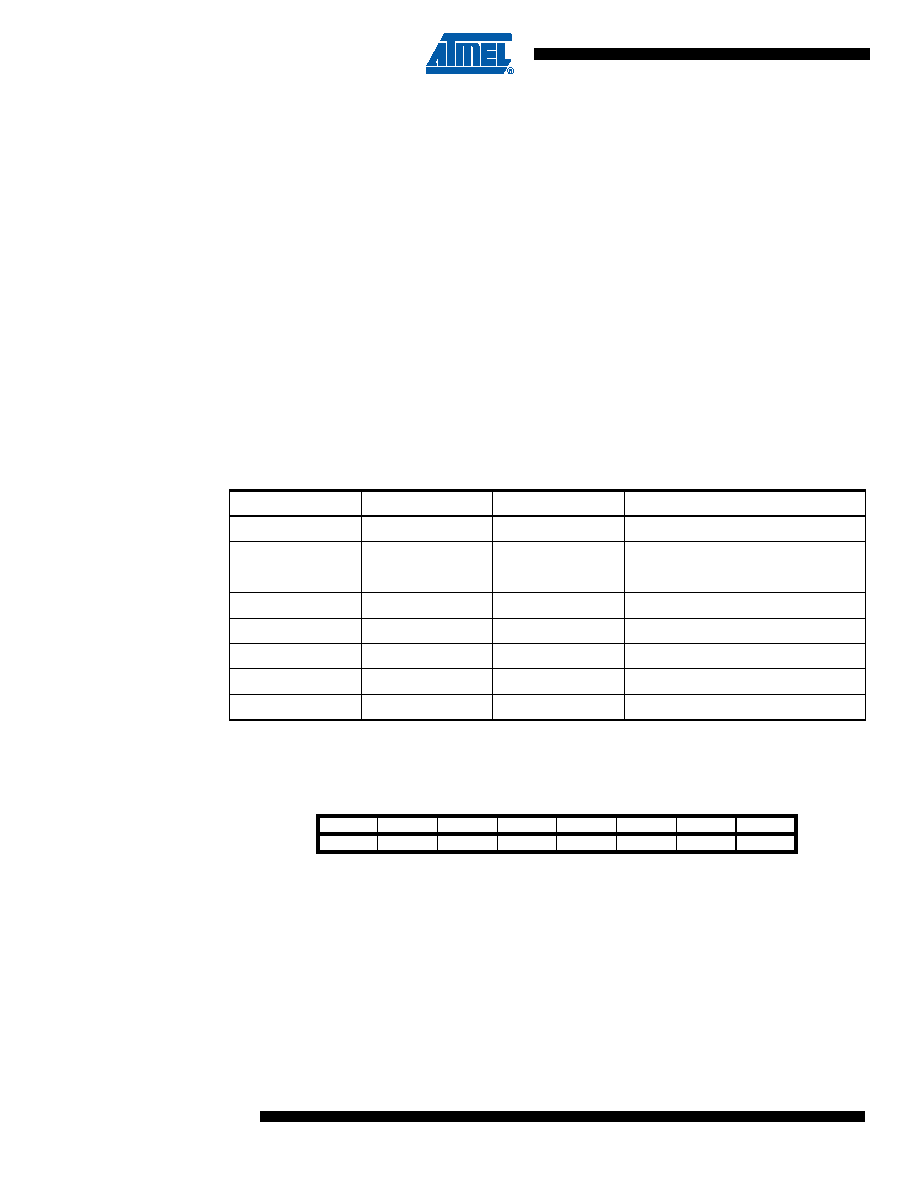

Table 16-5.

ADC Prescaler Selections

ADPS2

ADPS1

ADPS0

Division Factor

000

2

001

2

010

4

011

8

100

16

101

32

110

64

111

128

Bit

151413121110

9

8

–

ADC9

ADC8

ADCH

ADC7

ADC6

ADC5

ADC4

ADC3

ADC2

ADC1

ADC0

ADCL

765

43

21

0

Read/Write

R

RR

R

Initial Value

0

000

00

0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F727-E/P

IC PIC MCU FLASH 8KX14 40-DIP

PIC16F871T-E/PT

IC MCU CMOS 20MHZ 2K FLSH 44TQFP

PIC16F871T-E/L

IC MCU CMOS 20MHZ 2K FLSH 44PLCC

PIC16F871-E/PT

IC MCU CMOS 20MHZ 2K FLSH 44TQFP

PIC16F871-E/L

IC MCU CMOS 20MHZ 2K FLSH 44PLCC

PIC16F870T-E/SS

IC MCU CMOS 20MHZ 2K FLSH 28SSOP

PIC16F870T-E/SO

IC MCU CMOS 20MHZ 2K FLSH 28SOIC

PIC16F84AT-20E/SS

IC MCU CMOS 20MHZ 1K FLSH 20SSOP

相关代理商/技术参数

PIC16F872T-E/SS

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F872T-I/SO

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F872T-I/SS

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F872T-I/SS033

制造商:Microchip Technology Inc 功能描述:

PIC16F873-04/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F873-04/SO

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16F873 SOIC28

PIC16F873-04/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F873-04/SP

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F873 SDIL28